# KiCAD (/'kiːˌkæd/ KEE-kad)

#### What is KiCAD

- KiCAD lets you design your own PCB and is a type of software known as Electronic Design Automation (EDA).

- KiCAD is open source and free.

- Alternatives: Autodesk EAGLE, Altinum Designer, EasyEDA

## Fabrication companies

The following are companies I have used. Not an endorsement. Many fabrication companies exists.

- JLCPCB <u>https://jlcpcb.com/</u>

- OSHPark <u>https://oshpark.com/</u>

## JLCPCB

- Ships from China

- \$2 USD for 2 layers, up to 100mmx100mm, 5 pieces

- FR-4 Tg140, HASL plating

- Multiple board thickness and solder mask colors to choose from

- Many add-on options

- Order number is printed on PCB (removable with added cost)

- Higher quality boards, plating, options are available, but comes at a higher cost

## **OSHPark**

- Ships from USA

- \$5 USD / Square Inch, 3 pieces

- Free shipping option (even for Canada)

- FR4 175Tg, ENIG plating (gold)

- 1.6mm, 8mm and flex boards

- Purple solder mask

- Produced boards have tabs that need to be filed off

# KiCAD UI

- KiCAD is a collection of applications

- KiCAD is shortcut key driven, get used to it!

- Shortcut keys are different between programs

Schematic Editor Edit the project schematic

**PCB Editor** Edit the project PCB design

Footprint Editor Edit global and/or project PCB footprint libraries

**Gerber Viewer** Preview Gerber files

Image Converter Convert bitmap images to schematic symbols or PCB footprints

**Calculator Tools** Show tools for calculating resistance, current capacity, etc.

#

**Drawing Sheet Editor** Edit drawing sheet borders and title blocks for use in schematics and PCB designs

#### Plugin and Content Manager

Manage downloadable packages from KiCad and 3rd party repositories

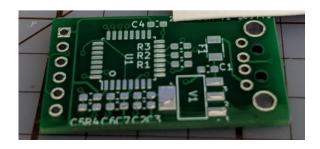

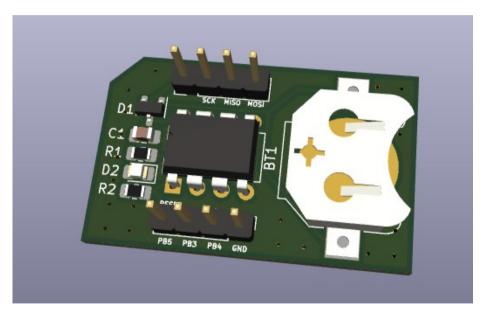

### Demo

- ATTiny85 breakout board

- 1 LED

- Breadboard compatible headers

#### **Reference Designators**

- Uniquely identify components on a board

- Usually consists of one or two letters and a number

- Common examples:

- R1, R2, ... Resistors

- D1, D2, ... Diodes

- C1, C2, ... Capacitors

- Q1, Q2, ... Transistors

- U1, U2, ... ICs

- F1, F2, ... Fuses

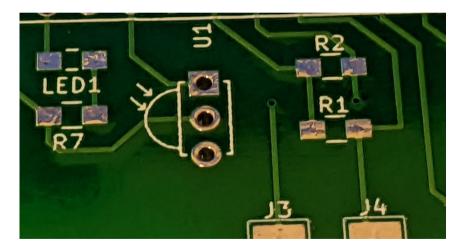

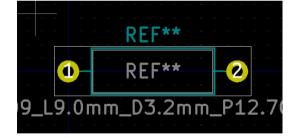

#### Footprints

- Template that defines the physical layout of the pads in a component

- Components have many variations: THT, SMD, DIP, etc.

0603 resistor

1206 resistor

Through hole resistor

# Electrical Rules Checker (ERC)

- Basic check on your schematics for errors

- Doesn't catch everything. Rely on yourself to avoid mistakes.

# **Design Rules**

- Enforce basic rules to meet the design requirements by the PCB fabrication company.

- Rules are different from company to company. Obtain the design rules from the fabrication company by checking their website.

- Even within the same fabrication company, the rules may be different based on the type of board. Always check the website.

#### **Netclass Editor**

• Specify clearances, trace widths, via diameters by defining net classes

| Net Class                                         | Clearance | Track Width | Via Size      | Via Hole | µVia Size     | uVia Hole | DP Width | DP Ga     |

|---------------------------------------------------|-----------|-------------|---------------|----------|---------------|-----------|----------|-----------|

| Default                                           | 0.2 mm    | 0.25 mm     | 0.8 mm        | 0.4 mm   | 0.3 mm        | 0.1 mm    | 0.2 mm   | 0.25 mm   |

| Power                                             | 0.2 mm    | 0.3 mm      | 0.8 mm        | 0.4 mm   | 0.3 mm        | 0.1 mm    | 0.2 mm   | 0.25 mm   |

|                                                   |           |             |               |          |               |           |          |           |

| +                                                 |           |             |               |          |               |           |          |           |

| Filter Nets                                       |           |             |               | Net      |               |           |          | Net Class |

| Net class filte                                   | er:       |             |               | ▼ /5∨    |               |           |          |           |

| Net name filt                                     | er:       |             |               | /РВС     | )             |           |          | Default   |

|                                                   |           |             |               | /PB1     |               |           |          | Default   |

| Show All Nets                                     |           |             | Apply Filters |          | 2             |           |          | Default   |

|                                                   |           |             |               | /PB3     | }             |           |          | Default   |

|                                                   |           |             |               | /PB4     | ł             |           |          | Default   |

| Assign Net Class                                  |           |             |               | /РВ      | 5             |           |          | Default   |

| New net class:                                    |           |             | - GND         | )        |               |           | Power    |           |

|                                                   |           |             |               | Net-     | (BT1-Pad1)    |           |          | Default   |

| Assign To All Listed Nets Assign To Selected Nets |           |             |               | ts Not-  | Net-(C1-Pad1) |           |          | Default   |

# Layers (2-layer PCB)

- F.Cu, B.Cu

- F.Paste, B.Paste

- F.SilkS, B.SilkS

- F.Mask, B.Mask

- Edge.Cuts

- F.CrtYd, B.CrtYd

- F.Fab, B.Fab

Copper layers Solder paste layers Silkscreen Solder mask PCB board outline Courtyard layers Fabrication layers

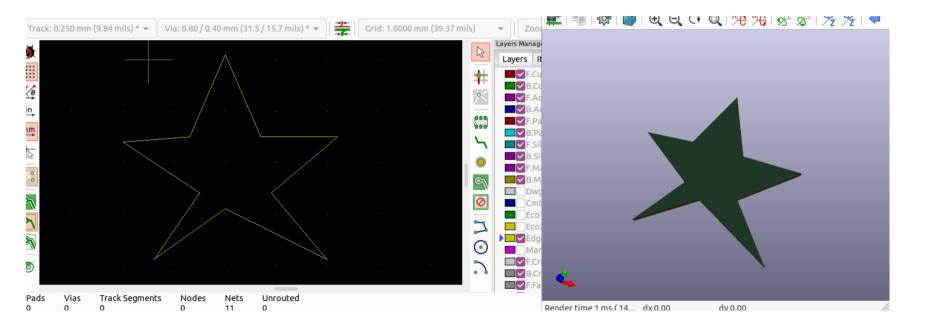

# Edge Cuts

• Define the shape of your PCB

# Autorouting

- KiCAD does not natively support auto-routing

- https://freerouting.org/ Standard alone auto-router which can be used

- Download it from: https://github.com/freerouting/freerouting/releases

# Gerbers

- Final file format for PCB production

- File  $\rightarrow$  Plot...

- Consult fabrication company for best options

|                                                                                 | Plo                                | ot (                                                                                                         |

|---------------------------------------------------------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------|

| Plot format:                                                                    | erber 👻 Output directory:          |                                                                                                              |

| nclude Layers                                                                   | General Options                    |                                                                                                              |

| F.Cu                                                                            | Plot border and title block        | Drill marks: None 👻                                                                                          |

| B.Cu<br>F.Adhesive                                                              | Plot footprint values              | Scaling: 1:1 -                                                                                               |

| <ul> <li>B.Adhesive</li> <li>F.Paste</li> </ul>                                 | Plot reference designators         | Plot mode: Filled 👻                                                                                          |

| B.Paste                                                                         | Force plotting of invisible values | / refs Use drill/place file origin                                                                           |

| F.Silkscreer<br>B.Silkscreer                                                    | Plot Edge Cuts on all lavers       | Mirrored plot                                                                                                |

| F.Mask                                                                          | Sketch pads on fabrication layer   | s 🗌 Negative plot                                                                                            |

| B.Mask                                                                          | gs Do not tent vias                | Check zone fills before plotting                                                                             |

| User.Eco2<br>Edge.Cuts<br>Argin<br>F.Courtyard<br>B.Courtyard<br>F.Fab<br>B.Fab | derber operons                     | Coordinate format: 4.6, unit mm •<br>Use extended X2 format (recommended)<br>reen Include netlist attributes |

|                                                                                 |                                    | Disable aperture macros (not recommended                                                                     |

| Output Message<br>Show: 🗌 All                                                   | s                                  | Actions Infos Save                                                                                           |

|                                                                                 |                                    |                                                                                                              |

| Run DRC                                                                         |                                    | Generate Drill Files Close Plot                                                                              |